In questo focus riportiamo la prime realizzazioni di transistor a singolo elettrone (SET) basati su eterostrutture di silicio/germanio e dimensioni critiche in scala nanometrica. L'evoluzione delle tecniche di fabbricazione dei circuiti LSI (Large Scale Integrated) ha portato ad una riduzione delle dimensioni dei dispositivi elettronici in scala submicronica. Parallelamente si è avuto un grande aumento della velocità di operazione di questi circuiti e del loro numero per unità di superficie. Attualmente, si utilizza la tecnologia CMOS che richiede migliaia di elettroni per definire il singolo bit. La continua miniaturizzazione dei dispositivi elettronici rende le fluttuazioni statistiche del numero di elettroni sempre più importanti impedendo una chiara definizione del bit. Nei transistor a singolo elettrone grazie agli effetti di bloccaggio coulombiano è possibile controllare il trasporto degli elettroni con la precisione di un elettrone. I SET quindi possono essere usati in circuiti nei quali il numero di elettroni per bit è di alcuni elettroni.

Presso l'Istituto di Fotonica e Nanotecnologie vengono realizzati dispositivi SET basati

su un processo litografico di tipo "top-down" a partire da un gas bidimensionali di elettroni ad alta mobilità in eterostrutture a modulazione di drogaggio di SiGe su Si. L'originalità del lavoro risiede nell'uso di eterostrutture di SiGe depositate epitassialmente su substrati di silicio. Il SiGe ha il grande vantaggio di essere compatibile e integrabile con la tecnologia del silicio, su cui è basata la microelettronica commerciale, e contemporaneamente la realizzazione di eterostrutture permette di utilizzare le proprietà specifiche di questi materiali quali la discontinuità di banda, la elevata mobilità dei portatori e la "band gap engineering".

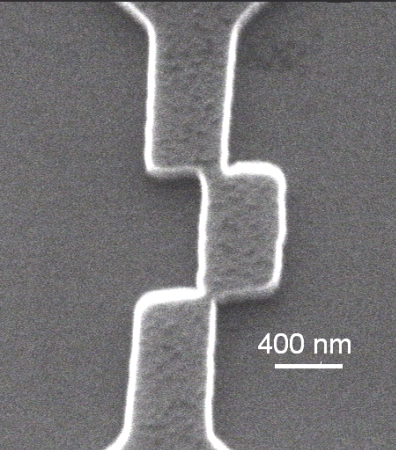

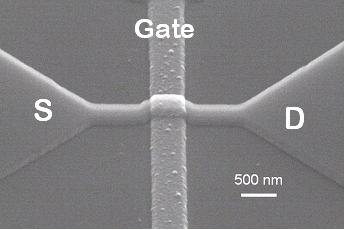

L'architettura proposta e realizzata per la fabbricazione del dispositivo, basata su una geometria a "filo curvato", (vedi figure) è originale e potenzialmente scalabile con le dimensioni geometriche, con conseguente innalzamento della temperatura di funzionamento del transistor.

Le barriere tunnel che delimitano la regione attiva del dispositivo (isola coulombiana) sono costituite da costrizioni geometriche del filo ottenute mediante una traslazione della regione centrale del filo stesso. L'entità della traslazione è inferiore alla larghezza del filo in modo che l'isola rimanga connessa alle estremità del filo, che agiscono da terminali di source e di drain, attraverso le due strozzature formate dalla traslazione. La caratterizzazione elettrica di questi SET è stata effettuata alla temperatura di 4.2 K e si è osservato il caratteristico diagramma di stabilità a diamanti di un transistor a singolo elettrone. In questo dispositivo sono stati misurati effetti di singola carica ben al di sopra delle temperatura dell'elio liquido, fino a circa 40 K.

Lo studio delle proprietà di trasporto, oltre ad evidenziare tutte le caratteristiche dei fenomeni a singola carica, ha sottolineato come in queste tipologie di materiali la natura del bloccaggio coulombiano sia di tipo stocastico e come questa caratteristica sia connessa in modo intrinseco alla complessità dell'eterostruttura.

Immagini: